### Description

The CV8013NK is a high efficiency, Qi-compliant wireless power receiver, targeted for 5W portable applications. The CV8013NK converts an AC power signal from a resonant tank into a regulated DC output voltage with 5V. Which integrated Low RDS(on) synchronous rectifier and ultra-low dropout offer high efficiency making the product ideally suited for battery-operated applications.

CV8013NK integrated an 1T-8051 Microprocessor offering a high level of program ability, an 12bit high precise ADC, a programmable current limit. High integration, To minimizing the external component count and cost effective solution. Work with different WPC compliance transmitter (TX), CV 8013 can deliver 5W.

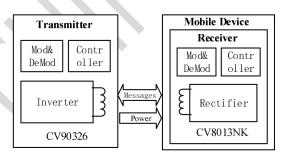

#### Wireless power system

Figure 1 CVS Wireless Power System

#### Features

- Single-chip RX solution supporting up to 5W application

- Compatible with WPC v1.2.4 Qi Standard

- Internal Integrated High efficiency Synchronous Rectifier

- Up to 83% peak DC-DC efficiency with CV90326

TX

- Programmable current limit

- Embedded Microprocessor

- Over voltage, over current, over temperature protection

- Integrated AD-Enable for wireless by-pass

- ~20 to +85°C ambient operating temperature range

- QFN32 (5mm x 5mm; 0.5mm pitch)

### **Typical Applications**

- Wireless power RTx solution for portable devices

- Mobile phone

- TWS Earbuds

- E-cigarettes

- Tablets

- Accessories

- Stationary device power supply

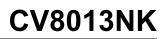

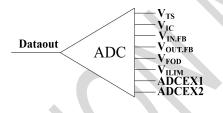

### 1. Block diagram

Figure 2 Block diagram of CV8013NK

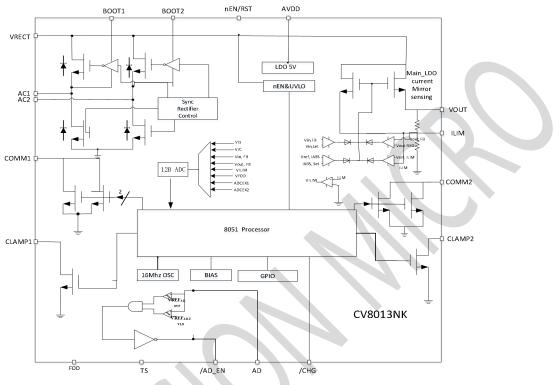

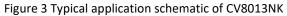

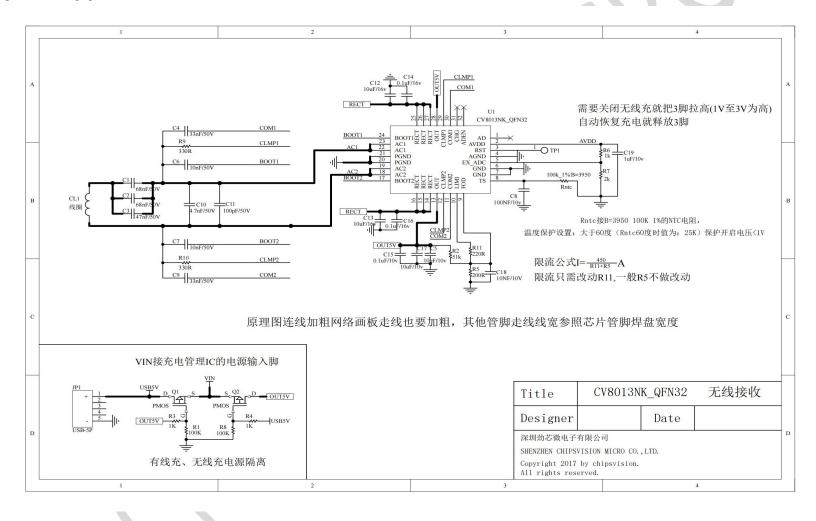

### **1.1 Typical Application Circuit**

Version 2.0

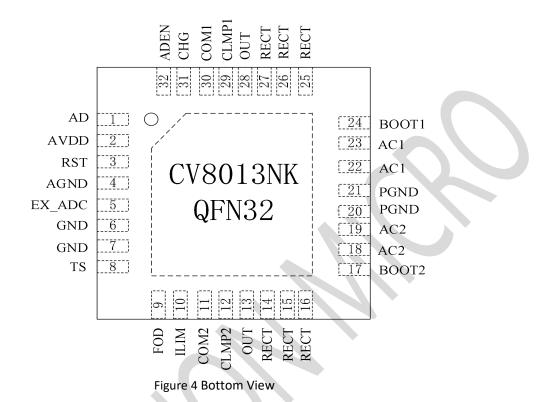

### 2. Pin Assignments

### 2.1 Pin configuration and functions

| PIN NO | PIN NAME | I/O | DESCRIPTION                                      |  |  |  |

|--------|----------|-----|--------------------------------------------------|--|--|--|

| 1      | AD       | -   | Adapter sense pin.                               |  |  |  |

| 2      | AVDD     | Р   | Supply voltage                                   |  |  |  |

| 3      | RST      |     | Chip disable, Pull High voltage to stop wireless |  |  |  |

| 3      |          |     | charging                                         |  |  |  |

| 4      | AGND     | Р   | Ground                                           |  |  |  |

| 5      | EX_ADC   | I   | Minimum voltage configuration                    |  |  |  |

| 6      | GND      | Р   | Ground<br>Ground                                 |  |  |  |

| 7      | GND      | Р   |                                                  |  |  |  |

| 8      | TS       | I   | Temperature sense, connect to NTC thermistor     |  |  |  |

|        |          |     | resistor                                         |  |  |  |

| 9      | FOD      | I   | Input pin to use for FOD calibration             |  |  |  |

| 10     | ILIM     | I/O | Programmable over-current limit pin. Connect to  |  |  |  |

| 10     | ILIIVI   | 1/0 | over-current protection resistor                 |  |  |  |

|        |          |     | Open drain output used to communication with     |  |  |  |

| 11     | COM2     | 0   | TX coil by varying reflected impedance. Connect  |  |  |  |

| **     |          |     | through a capacitor to either AC2 for capacitive |  |  |  |

|        |          |     | load modulation.                                 |  |  |  |

| PI | N NO | PIN NAME | I/O | DESCRIPTION                                                                                                                                                             |

|----|------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |      |          |     | When the Vrect voltage goes bove 15v, To                                                                                                                                |

|    | 12   | CLMP2    | 0   | connect on capacitance (or Resistor) to reduce                                                                                                                          |

|    |      |          |     | coupling for device protection.                                                                                                                                         |

|    | 13   | OUT      | 0   | Output pin, used to deliver power to the load                                                                                                                           |

|    | 14   | RECT     | о   | Filter capacitor for synchronous rectifier .                                                                                                                            |

|    | 15   | RECT     | 0   | Filter capacitor for synchronous rectifier .                                                                                                                            |

|    | 16   | RECT     | 0   | Filter capacitor for synchronous rectifier                                                                                                                              |

|    | 17   | BOOT2    | 0   | Bootstrap capacitors for driving the high side<br>FETs of the synchronous rectifier. Connect a 10nF<br>capacitor from BOOT2 to AC2.                                     |

|    | 18   | AC2      | I   | AC input power via external coil                                                                                                                                        |

|    | 19   | AC2      | I   | AC input power via external coil                                                                                                                                        |

|    | 20   | PGND     | Р   | Ground                                                                                                                                                                  |

|    | 21   | PGND     | Р   | Ground                                                                                                                                                                  |

|    | 22   | AC1      | I,  | AC input from receiver coil                                                                                                                                             |

|    | 23   | AC1      | 1   | AC input from receiver coil                                                                                                                                             |

|    | 24   | BOOT1    | 0   | Bootstrap capacitors for driving the high side<br>FETs of the synchronous rectifier. Connect a 10nF<br>capacitor from BOOT1 to AC1                                      |

|    | 25   | RECT     | 0   | Filter capacitor for synchronous rectifier                                                                                                                              |

|    | 26   | RECT     | 0   | Filter capacitor for synchronous rectifier                                                                                                                              |

|    | 27   | RECT     | ο   | Filter capacitor for synchronous rectifier                                                                                                                              |

|    | 28   | ОИТ      | 0   | Power output, used to deliver power to the load                                                                                                                         |

|    | 29   | CLMP1    | 0   | When the Vrect voltage goes bove 15v, To<br>connect on capacitance (or Resistor) to reduce<br>coupling for device protection.                                           |

|    | 30   | COM1     | 0   | Open drain output used to communication with<br>TX coil by varying reflected impedance. Connect<br>through a capacitor to either AC1 for capacitive<br>load modulation. |

|    | 31   | /CHG     | 0   | Charging indicator.                                                                                                                                                     |

|    | 32   | /AD_EN   | О   | Push-pull driver for dual PFET circuit that can<br>pass AD input to the OUT pin; Used for adapter<br>MUX control.                                                       |

### 3. Electrical characteristics

#### 3.1 Absolute Maximum Rating

| Parameter               | Condition           | MIN  | ТҮР | MAX  | UNIT   |

|-------------------------|---------------------|------|-----|------|--------|

| Input Voltage           | CHG,FOD,TS,ILIM,OUT | -0.3 |     | 7    | V      |

| input voitage           | Other Pins          | -0.3 |     | 20   | V      |

| Input Current           | AC1, AC2            |      |     | 2    | A(RMS) |

| Output Current          | OUT                 |      |     | 1.25 | А      |

| Junction<br>Temperature |                     |      |     | 150  | °C     |

| ESD(HBM)                | All pins            |      |     | 2    | kV     |

#### 3.2 Thermal characteristics

| Parameter | Description                            | MIN | ТҮР | МАХ | UNIT |

|-----------|----------------------------------------|-----|-----|-----|------|

| ΑιΘ       | Junction to ambient thermal resistance |     | 47  |     | ≌C/W |

### 3.3 Recommend characteristics

| Parameter         | Description          | MIN | ТҮР | ΜΑΧ | UNIT |

|-------------------|----------------------|-----|-----|-----|------|

| RCET              | Input voltage range  |     |     | 12  | V    |

| l <sub>in</sub>   | Input current        |     |     | 1.5 | А    |

| Ιουτ              | Output current       |     |     | 1   | А    |

| І <sub>сомм</sub> | COMM current         |     |     | 0.5 | А    |

| Tı                | Junction Temperature | 0   |     | 125 | °C   |

#### 3.4 Electrical characteristics

| Parameter                 | Description                                  | MIN                    | ТҮР | МАХ                   | UNIT |

|---------------------------|----------------------------------------------|------------------------|-----|-----------------------|------|

| UVLO                      | Under-voltage lock out                       |                        | 5   | 5.1                   | V    |

| V <sub>RECT(OVP)</sub>    | V <sub>RECT</sub> over voltage protection    |                        | 12  |                       | V    |

| V <sub>RECT(REG)</sub>    | V <sub>RECT</sub> range set by communication | V <sub>OUT</sub> +0.12 |     | V <sub>OUT</sub> +2.0 | V    |

| V <sub>OUT(REG)</sub>     | Regulated output voltage                     |                        | 5.0 |                       | V    |

| Ι <sub>ουτ</sub>          | Output current range                         |                        | 1   |                       | А    |

| V <sub>TS</sub>           | Temperature sense bias voltage               | 4.5                    | 5.0 | 5.5                   | v    |

| R <sub>TS</sub>           | Pull-up resistor for TS to bias voltage      | 90                     | 100 | 110                   | kΩ   |

| T <sub>J(SHUTDOWN)</sub>  | Thermal shutdown temperature                 |                        | 150 |                       | ₅C   |

| T <sub>J(HYS)</sub>       | Thermal shutdown hysteresis                  |                        | 20  |                       | °C   |

| R <sub>ds(on,com)</sub>   | COM1 and COM2                                |                        | 1.0 |                       | Ω    |

| f <sub>сомм</sub>         | Communication frequency                      |                        | 2.0 |                       | kb/s |

| R <sub>ds(on,clamp)</sub> | CLAMP pin MOSFET                             |                        | 0.5 |                       | Ω    |

### 4. Function description

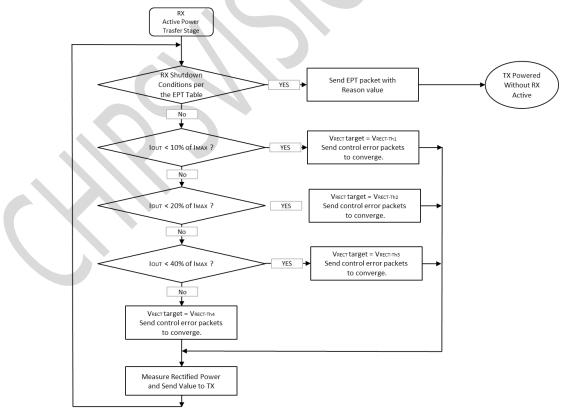

#### 4.1 Sync Rectifier

Dynamic rectifier adjust the purpose is to optimize efficiency and reduce the overall LDO

power consumption

$P_{DIS} = (V_{RECT} - V_{OUT})^* I_{OUT}$

The rage of dynamic adjustment is as follows (see table below)

| Output Current Percentage | V <sub>RECT</sub> (V)          |

|---------------------------|--------------------------------|

| 0~10%                     | V <sub>OUT</sub> + 2.00        |

| 10%~20%                   | V <sub>OUT</sub> + 1.5         |

| 20%~40%                   | V <sub>OUT</sub> + <b>0.56</b> |

| >40%                      | V <sub>OUT</sub> + 0.12        |

Wherein,  $I_{\text{OUT}}$  current percentage is determined according to the maximum output current  $I_{\text{MAX}}$

setting by RILIM.

V<sub>RECT</sub> Dynamic adjustment is accomplished by the controlling program of RXthrough communicating

with TX. Control flow chart is as below.

Version 2.0

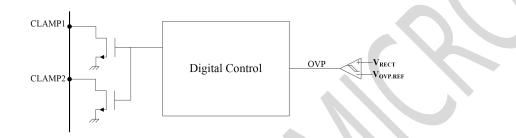

#### 4.2 VRECT Over-voltage protection

VRECT through internal comparator, generate over-voltage signal OVP and send the OVP signal to digital logic. Digital logic sends OVP interrupts to MCU. RX controlling program drives CLMP pin to cause RX coil to be detuned to reduce the amount of the received energy. Thereby, rapidly reduce VRECT to a safe range.

#### 4.3 VRECT relevant parameters

| Parameter              | Description                               | MIN                    | ТҮР | MAX                   | UNIT |

|------------------------|-------------------------------------------|------------------------|-----|-----------------------|------|

| V <sub>RECT(REG)</sub> | V <sub>RECT</sub> range set by COMM       | V <sub>OUT</sub> +0.12 |     | V <sub>OUT</sub> +2.0 | V    |

| VRECT(TRACK)           | V <sub>RECT</sub> above V <sub>OUT</sub>  |                        | 120 |                       | mV   |

| V <sub>OVP,REF</sub>   | V <sub>RECT</sub> over voltage protection |                        | 12  |                       | V    |

| R <sub>DS(ON)</sub>    | CLAMP pin MOSFET                          |                        | 0.5 |                       | Ω    |

#### 4.4 LDO

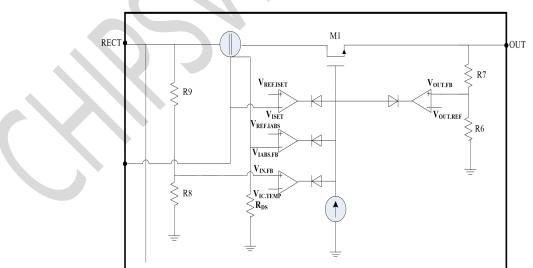

LDO schematic diagram is as above. The functions of the 4 amplifiers are as follows.

#### 4.5 VOUT, FB

V<sub>OUT</sub> is fed back to the amplifier negative input through a resistor divider network and compare

with the internal default setting to control M1 to output the stable voltage.

The relevant parameters are as follows:

| Parameter              | Description                     | MIN     | ТҮР    | MAX     | UNIT |

|------------------------|---------------------------------|---------|--------|---------|------|

| K <sub>RO</sub>        | Feedback Resistor Ratio         | 1.2/8.0 |        | 1.2/4.5 |      |

| V <sub>OUT,REG</sub>   | V <sub>OUT</sub> Reference      |         | 1.2174 |         | V    |

| I <sub>OUT, MAX</sub>  | Max Current Limit               |         |        | 125     | A    |

| I <sub>OUT</sub> , dis | Quiescent Current when disabled |         | 20     | 35      | μΑ   |

#### 4.6 VILIM

The  $R_{ILIM}$ , is the external resistor connected with ILIM pin. The voltage sampling value  $V_{ILIM}$  input to the amplifier negative input pin and is compared with the reference voltage  $V_{ILIM,REF}$ . If the voltage value  $V_{ILIM}$  exceeds the threshold  $V_{ILIM,REF}$ , then reduce  $I_{OUT}$  output current by controlling M1.

The calculation of maximum output current I<sub>MAX</sub> is as follows:

RILIM=KILIM/IMAX

Considering 20% margin of the setting value  $I_{MAX}$ ,  $I_{ILIM}=1.2*I_{MAX}$ .  $R_{ILIM}$  is calculated by the following equation.

R<sub>ILIM</sub>=K<sub>ILIM</sub>/I<sub>LIM</sub>= K<sub>ILIM</sub>/1.2I<sub>MAX</sub>

The relevant parameters are as follows:

| Parameter             | Description                | MIN | ТҮР | ΜΑΧ | UNIT |

|-----------------------|----------------------------|-----|-----|-----|------|

| K <sub>ilim</sub>     | Current Limit Factor       |     | 450 |     | Ω    |

| V <sub>ILIM,REF</sub> | I <sub>LIM</sub> Reference |     | 1.2 |     | V    |

#### 4.7 End Power Transfer Package (WPC Header 0x02)

The WPC allows for special commands for the receiver to terminate power transfer from the Version 2.0

transmitter termed End Power Transfer (EPT) packet. The table below specifies the V1.2 reasons

column and their corresponding data field value. The condition column corresponds to the

methodology used by CV8013NK to send equivalent message.

| MESSAGE          | VALUE | CONDITION                                                       |

|------------------|-------|-----------------------------------------------------------------|

| Unknown          | 0x00  | AD>3.6V                                                         |

| Charge complete  | 0X01  | TS/CTRL <0.3V; charge complete                                  |

| Internal Fault   | 0x02  | Vic,TEMP: Vic_TEMP>Vj,Off                                       |

| Over temperature | 0x03  | TS < VHOT                                                       |

| Over voltage     | 0x04  | NOT Send, Send 0x03 code to reduce power transfer in this case. |

| Over current     | 0x05  | Not Send                                                        |

| Battery Failure  | 0x06  | Not Send                                                        |

| Reconfigure      | 0x07  | Not Send                                                        |

| No Response      | 0x08  | Once Vrect voltage cannot reach 6.5V                            |

#### 4.8 Adapter Enable

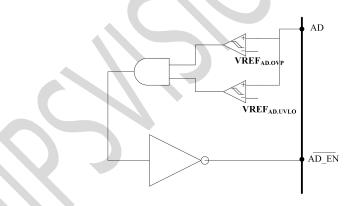

In order to be compatible with external adapter plugged in, AD pins are used to monitor the input voltage of adapter. When AD is above VREF<sub>AD,OVP</sub>, means external adapter is plugged in. Internal comparatorpulls AD\_EN pin to logic low. AD\_EN at logic low drives external PMOS to enable the wired charging path. Meanwhile, AD\_EN signal is sent to digital logic, RX control program sends EPT to notify TX to stop power transmission. If AD\_EN is below VREF<sub>AD,OUVLO</sub>, means external adapter is unplugged. Internal cooperator pulls AD\_EN pin to logic high, cut off the wired charging path and the chip.

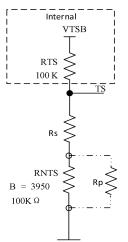

#### 4.9 External Temperature Sense

TS pin is used to monitor the external temperature by using NTC resistor network. Internal pull-up resistor  $V_{TSB}$  RTS and external resistor composes voltage division circuit. The internal ADC converts the value of  $V_{TS}$  voltage. And the over temperature protection will be triggered when the  $V_{TS}$  less then 1V. the RX will send EPT (end power transfer) package to TX, and stop to output.

\*To revise Rs and Rp resistors to change over temperature protection (OTP) trigger point setting,

Rs= $0 \Omega$ , Rp: NC, the OTP trigger point is  $60^{\circ}$  C;

The calculation formula is as follow:

(5V\*Rntc)/(RTS+Rntc)=1V

To rise Rs resistance value, the OTP trigger point will be rised (>60 $^{\circ}$  C);

To select resistor value for Rp to set OTP triggle point (<60° C);

The related parameters are as follows:

| Parameter        | Description              | MIN | ТҮР | MAX | UNIT |

|------------------|--------------------------|-----|-----|-----|------|

| V <sub>TSB</sub> | Internal TS Bias Voltage |     | 5   |     | V    |

| R <sub>TS</sub>  | Pullup Resistor for NTC  |     | 100 |     | kΩ   |

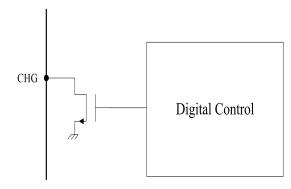

4.10 Charging Status

Digital logic drives CHG pin to notify external system that IOUT is being output, indicating that

wireless charging is in progress.

#### 4.11 Internal ADC

ADC input 8 sets internal voltage signals and sends to digital logic after digital-to-analog conversion. RX control program make the corresponding detection and judgment.

| Input Signal         | Dut Signal Description             |     |

|----------------------|------------------------------------|-----|

| V <sub>TS</sub>      | External Temperature Sense Voltage | TBD |

| V <sub>IC,TEMP</sub> | Internal Temperature Sense Voltage | TBD |

| V <sub>IN,FB</sub>   | V <sub>RECT</sub> Feedback Voltage | TBD |

| V <sub>OUT,FB</sub>  | V <sub>OUT</sub> Feedback Voltage  | TBD |

| V <sub>FOD</sub>     | I <sub>OUT</sub> sample Voltage    | TBD |

| VILIM                | I <sub>LIM</sub> sample Voltage    | TBD |

| ADCEX1               | External Analog Signal1            | TBD |

| ADCEX2               | ADCEX2 External Analog Signal2     |     |

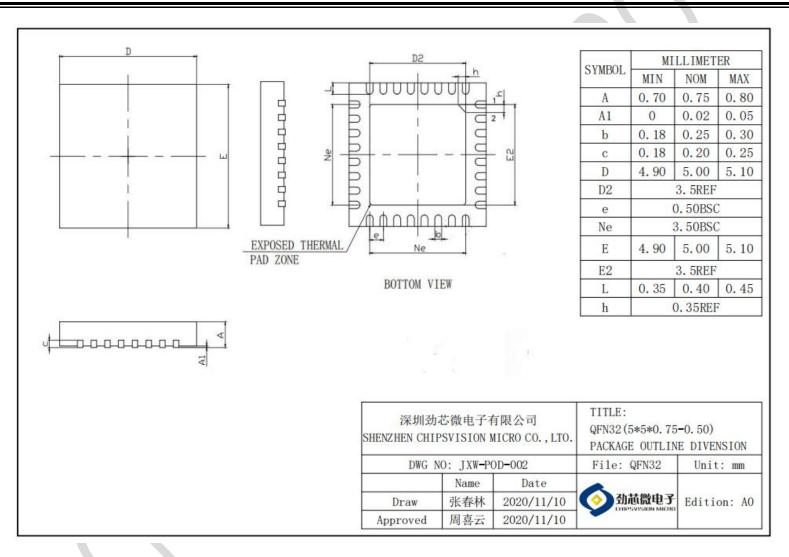

### 5. Package information

| Orderable Part<br>Number | Description and Package        | MSL<br>Rating | Shipping<br>Packagin<br>g | Ambient<br>Temperatur<br>e |

|--------------------------|--------------------------------|---------------|---------------------------|----------------------------|

| CV8013NK                 | QFN32 (5mm x 5mm; 0.5mm pitch) | MSL3          | Tape and reel             | 0°C to +85°C               |

Note: The package outline drawings is on page 14 of this document.

Version 2.0

### 6. Typical Application Schematics

Version 2.0