### Wireless Power Transmitter for Smartphones with 15W Application

#### 1 Description

The CV90330 is a wireless power transmitter controller that integrates all required functions for the WPC "Qi" compliant wireless power transmitter design.which supports various adapters such as QC2.0, QC3.0, AFC and so on.Compliance with the latest WPC V1.2 standard, support MP-A11 coil,support customer coil customized solution, support BPP 5W, Apple 7.5W, Samsung 10W, EPP 15W charging.

The CV90330 has Integrated over voltage protection, over current protection, over temperature protection and other functions, and supports FOD detection.

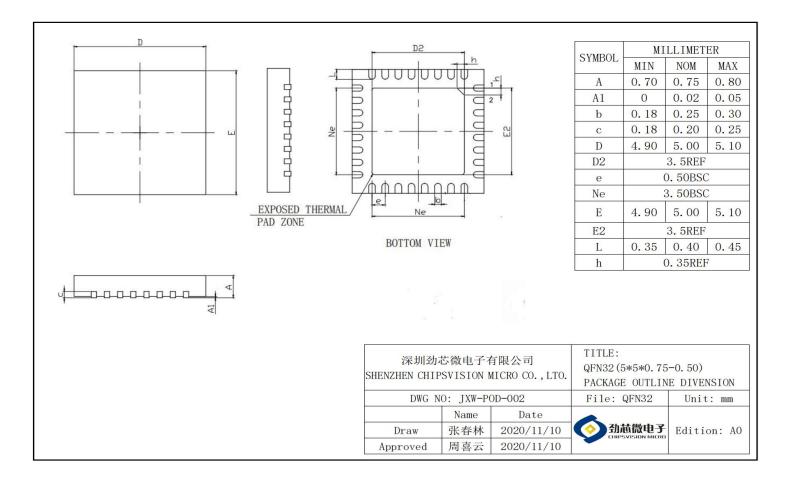

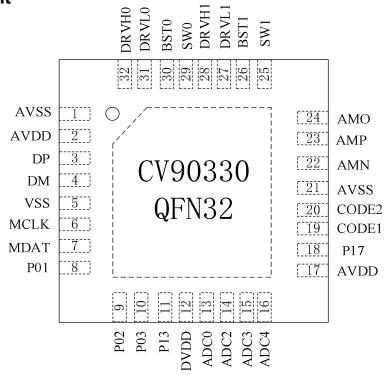

The CV90330 is a QFN32 package, and integrates full bridge drive circuit and voltage & current communication decoding function module, which can significantly reduce PCB size and BOM cost.

## 2 Typical Applications

- $\stackrel{\wedge}{\leadsto}$  BPP and EPP wireless charging pads

- $\cancel{2}$  Android fast charging pads

- ☆ Tablets

- $\cancel{2}$  Up to 7.5W charging for iPhones

#### 3 Features

- WPC 1.2.4 compatible

- Power transfer up to 15W in EPP mode

- 16kB Multiple-time programmable (MTP) non-volatile memory for expanded feature support

- Integrated drivers for external power MOSFETs

- Real-time foreign object detection (FOD)

- Over voltage , over temperature and over current protection

- Supports I2C interface

- Integrated voltage and current sense amplifier

- LED for system status indication

- Operating temperature: -40 °C up to 85 °C

## **4 Product Information**

| Orderable<br>Part Number | Package<br>Type | Package Size          |

|--------------------------|-----------------|-----------------------|

| CV90330                  | QFN32           | 5.00 * 5.00 * 0.75 mm |

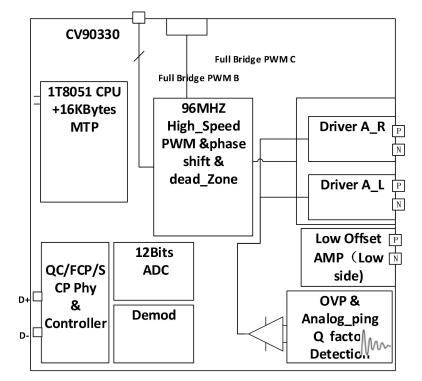

## **1.** Function block diagram

#### 1.1 Chip Block diagram

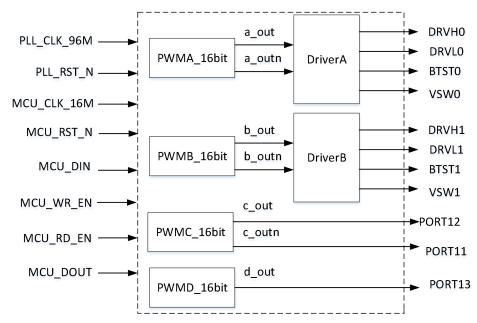

#### **1.2 PWM generator Architecture**

PWM A&B with the MOS deivers can driver a full bridge inverter, PWMC and external power stage to compose another full bridge driver to drive one coils, the single end PWMD is a controller for voltage regulating solution.

Version 1.1

#### 2. Pin Assignment

#### **2.1 Pin Descriptions**

| Pin No. | Name | Description                                               |

|---------|------|-----------------------------------------------------------|

| 1       | AVSS | Ground                                                    |

| 2       | AVDD | Power source                                              |

| 3       | DP   | USB D+ interface                                          |

| 4       | DM   | USB D- interface                                          |

| 5       | VSS  | Ground                                                    |

| 6       | MCLK | Emulation port clock pin                                  |

| 7       | MDAT | Emulation port data pin                                   |

| 8       | P01  | General-purpose digital I/O pin<br>External interrupt PIN |

| 9       | P02  | General-purpose digital I/O pin<br>Serial 0 transmit data |

| 10      | P03  | General-purpose digital I/O pin                           |

| 11      | P13  | General-purpose digital I/O pin<br>Count/Capture 0        |

Version 1.1

|    |       | PWMD single end PWM output for voltage regulating control |

|----|-------|-----------------------------------------------------------|

| 12 | DVDD  | VDD1.8V                                                   |

| 13 | ADC0  | ADC input channel 0                                       |

| 14 | ADC2  | ADC input channel 2                                       |

| 15 | ADC3  | ADC input channel 3                                       |

| 16 | ADC4  | ADC input channel 4                                       |

| 17 | AVDD  | Supply voltage                                            |

| 18 | P17   | General-purpose digital I/O pin<br>I2C SDA<br>ADC         |

| 19 | CODE1 | Current sensing demodulation input                        |

| 20 | CODE2 | Voltage sensing demodulation input                        |

| 21 | AVSS  | GND                                                       |

| 22 | AMN   | Op-amp nagtive input terminal                             |

| 23 | AMP   | Op-amp postive input terminal                             |

| 24 | AMO   | Op-amp output terminal                                    |

| 25 | VSW1  | MOSFET Half-Bridge Driver 1 High-side source connection.  |

| 26 | BST1  | MOSFET Half-Bridge Driver 1 High-side bootstrap supply    |

| 27 | DRL1  | MOSET Half-Bridge Driver 1 Low-Side output                |

| 28 | DRH1  | MOSET Half-Bridge Driver 1 High-Side output               |

| 29 | VSW0  | MOSFET Half-Bridge Driver 0 High-side source connection.  |

| 30 | BST0  | MOSFET Half-Bridge Driver 0 High-side bootstrap supply    |

| 31 | DRL0  | MOSFET Half-Bridge Driver 0 Low-Side output               |

| 32 | DRH0  | MOSFET Half-Bridge Driver 0 High-Side output              |

#### **3.** Absolute MaximumRatings

The absolute maximum ratings are stress ratings only. Stresses greater than those listed in Table 2 and Table 3 can cause permanent damage to the CV90330. Functional operation of the CV90330 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions might affect device reliability.

#### **3.1 Absolute Maximum Ratings**

Note: All voltages are referenced to ground.

| Symbol/Pins                                                                                                                                                                              | Parameter                            | Conditions                                    | Minimu<br>m | Maximu<br>m | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------|-------------|-------------|-------|

| VSW1,BTS1,DRL1,D<br>RH1<br>VSW2,BTS2,DRL2,D<br>RH2                                                                                                                                       | Absolute Maximum Pin<br>Voltage      |                                               | -0.3        | 24          | V     |

| VDD,nRST,<br>OSCIN,OSCOUT,<br>P00,P02 ~ P06, P10,<br>P11<br>MDAT,MCLK<br>ADC1 ~ ADC5<br>AMP0+,AMP0-,AMP0<br>o<br>AMP1+,AMP1-,AMP1<br>o<br>AMP2+,AMP2-,AMP2<br>o<br>AMP3+,AMP3-,AMP3<br>o | Absolute Maximum Pin<br>Voltage      |                                               | -0.3        | 6           | V     |

| GND                                                                                                                                                                                      | Absolute Maximum Pin<br>Voltage      |                                               | -0.3        | 0.3         | V     |

| +1.8VO                                                                                                                                                                                   | Absolute Maximum Pin<br>Voltage      |                                               | -0.3        | 2           | V     |

| НВМ                                                                                                                                                                                      | ESD Rating – Human Body<br>Model     | All pins                                      | -2000       | 2000        | V     |

| CDM                                                                                                                                                                                      | ESD Rating – Charged<br>Device Model | All pins                                      | -500        | 500         | V     |

| TJ                                                                                                                                                                                       | Maximum Junction<br>Temperature      | See Table 3 for<br>important<br>restrictions. |             | 150         | °C    |

| T <sub>STOR</sub>                                                                                                                                                                        | Storage Temperature                  |                                               | -55         | 150         | °C    |

| T <sub>LEAD</sub>                                                                                                                                                                        | Lead Temperature<br>(soldering, 10s) |                                               |             | 300         | °C    |

#### **4.** Thermal Characteristics

#### **4.1 Thermal Characteristics**

| Symbol          | Parameter                                            | Value | Units |

|-----------------|------------------------------------------------------|-------|-------|

| θ <sub>JA</sub> | Thermal Resistance Junction to Ambient [a], [b], [c] | 27.2  | °C/W  |

| Version 1.1     |                                                      | 5     |       |

| θ <sub>JC</sub> | Thermal Resistance Junction to Case [a], [b], [c]             | 18.8 | °C/W |

|-----------------|---------------------------------------------------------------|------|------|

| $\theta_{JB}$   | Thermal Resistance Junction to Board <sup>[a], [b], [c]</sup> | 1.36 | °C/W |

[a] The maximum power dissipation is  $P_{D(MAX)} = (T_{J(MAX)} - T_{AMB}) / \theta_{JA}$  where  $T_{J(MAX)}$  is 125°C. (See Table 4.) Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the device will enter thermal shutdown.

- [b] This thermal rating was calculated on a JEDEC 51 standard 4-layer board with the dimensions 3" x 4.5" in still air conditions.

- [C] Actual thermal resistance is affected by PCB size, solder joint quality, layer count, copper thickness, air flow, altitude, and other unlisted variables.

### 5. Recommended OperatingConditions

#### Table4. Recommended OperatingConditions

| Symbol             | Parameter                                   | Minimu | Туріс | Maximu | Units |

|--------------------|---------------------------------------------|--------|-------|--------|-------|

|                    |                                             | m      | al    | m      |       |

| V <sub>IN</sub>    | Input Operating Range <sup>[a], [b]</sup>   | 4.5    | 5     | 5.5    | V     |

| V <sub>VDDIO</sub> | Input Voltage Supply Range for GPIO A and B | 1.8    |       | 2;5    | V     |

|                    | Banks                                       |        |       |        |       |

| TJ                 | Operating Junction Temperature [c]          | -40    |       | +125   | °C    |

| T <sub>AMB</sub>   | Ambient Operating Temperature [c]           | -40    |       | +85    | ۵°    |

<sup>[</sup>a] The input voltage operating range is dependent upon the type of transmitter power stage (full-bridge, half-bridge) and transmitting coil inductance. WPC specifications should be consulted for appropriate input voltage ranges by end product type.

- [b] The minimum for this specification is the minimum IC operating specification. Full power transfer will not occur at this level.

- [C] Important: Refer to Table 3 for important restrictions and notes.

## 6. Electrical Characteristics

#### **6.1 Electrical Characteristics**

$V_{IN} = 5V$ , Typical values are at 25°C, unless otherwise noted.

Note: See important notes at the end of the table.

| Symbol                      | Parameter            | Conditions            | Minimu | Туріс | Maximu | Units |  |  |

|-----------------------------|----------------------|-----------------------|--------|-------|--------|-------|--|--|

|                             |                      |                       | m      | al    | m      |       |  |  |

| Input Sup                   | Input Supplies       |                       |        |       |        |       |  |  |

| VIN                         | Input Operating      |                       | 3.3    | 5     | 5.5    | V     |  |  |

|                             | Range                |                       |        |       |        |       |  |  |

| I <sub>IN</sub>             | Operating Mode Input | Normal power transfer |        | 10    |        | mA    |  |  |

|                             | Current              | state                 |        |       |        |       |  |  |

| Analog to Digital Converter |                      |                       |        |       |        |       |  |  |

| Version 1.1                 | 1                    |                       |        |       | 6      |       |  |  |

| N                    | Resolution                     |                                  |    | 12  |    | Bit  |

|----------------------|--------------------------------|----------------------------------|----|-----|----|------|

| Channel              | Number of Channels             |                                  |    | 14  |    |      |

| V <sub>IN,FS</sub>   | Full Scale Input               |                                  |    | VDD |    | V    |

|                      | Voltage                        |                                  |    |     |    |      |

| Operation            | al Amplifiers                  |                                  | ÷  |     |    |      |

| V <sub>IO</sub>      | Input offset voltatge          | Vcc = 5V                         |    |     | 5  | mV   |

| l <sub>IO</sub>      | Input offset current           | Vo = 1.4V                        |    |     | 80 | nA   |

| CMMR                 | Common-mode<br>rejection ratio | V <sub>IC</sub> = 5V, 25°C       |    | 70  |    | dB   |

| SR                   | Slew rate at unity gain        | $R_L = 1M\Omega, C_L = 30pF$     |    | 0.5 | 5  | V/µS |

| BI                   | Unity-gain bandwidth           | $R_L = 1M\Omega, C_L = 20pF$     |    | 1.2 |    | MHz  |

| Vn                   | Equivalent input nose          | $R_s = 100\Omega, V_i = 0V, f =$ |    | 25  |    | nV/√ |

|                      | voltage                        | 1kHz                             |    | 35  |    | Hz   |

| LDO18 (Co            | υτ=1μF)                        |                                  | 1  | I   |    | 1    |

| V <sub>OUT18</sub>   | Output Voltage                 |                                  |    | 1.8 |    | V    |

| ΔVout/Vo             | Output Voltage                 |                                  |    | ±5  |    | %    |

| UT                   | Accuracy                       |                                  |    |     |    |      |

| IOUT18_MAX           | Maximum Output                 |                                  |    | 10  |    | mA   |

| _                    | Load Current                   |                                  |    |     |    |      |

| <b>Thermal S</b>     | hutdown                        |                                  | ÷  |     |    |      |

| <b>-</b>             | Thermal Shutdown               | Threshold Rising                 |    | 140 |    | °C   |

| T <sub>SD</sub>      |                                | Threshold Falling                |    | 120 |    | °C   |

| <b>Clock Osc</b>     | illators                       |                                  | ÷  |     |    |      |

| C                    | Internal RC-OSC                |                                  | 12 | 16  | 20 | МН   |

| F <sub>RC-OSC</sub>  | Clock Frequency                |                                  | 12 | 10  | 20 |      |

| F <sub>CRYSTAL</sub> | External Crystal Clock         |                                  | 12 | 20  | 24 | МН   |

| CRYSTAL              | Frequency                      |                                  | 12 | 20  | 24 |      |

| FSYSCLK              | OSC Clock                      |                                  | 12 | 16  | 24 | МН   |

| • SYSCLK             | Frequency                      |                                  | 12 |     | 24 |      |

|                      | Phase Lock-Loop                |                                  |    |     |    |      |

| F <sub>PLL-OUT</sub> | (PLL) Voltage                  |                                  | 12 | 84  | 96 | МН   |

| • 1 LL-001           | Controlled Oscillator          |                                  |    |     |    |      |

|                      | (VCO) Frequency <sup>[d]</sup> |                                  |    |     |    |      |

| Symbol           | Parameter             | Conditions                        | Minimu      | Туріс | Maximu   | Units |

|------------------|-----------------------|-----------------------------------|-------------|-------|----------|-------|

|                  |                       |                                   | m           | al    | m        |       |

| General Pu       | urpose Inputs/Outputs | (GPIO)                            | ·           |       |          |       |

| VIH              | Input HIGH Voltage    |                                   | 0.7<br>*VDD |       |          | V     |

| VIL              | Input LOW Voltage     |                                   |             |       | 0.3 *VDD | V     |

| I <sub>LKG</sub> | Leakage Current       |                                   | -1.0        |       | 1.0      | μA    |

| V <sub>OH</sub>  | Output Logic HIGH     | VDD = 5.0V, I <sub>OH</sub> = 8mA | 4.3         |       |          | V     |

| V <sub>OL</sub>  | Output Logic LOW      | VDD = 5.0V, I <sub>IH</sub> = 8mA |             |       | 0.7      | V     |

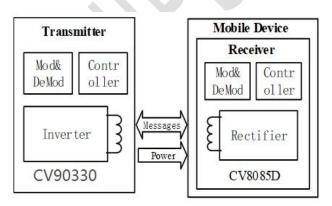

### 7. Theory of Operation

The CV90330 is a highly-integrated wireless power transmitter IC solution for mobile devices. It can transfer up to 15W of power in High-Speed- Charger Mode, such as QC2.0/QC3.0 mode or 5W (typical) in WPC mode from a wireless transmitter to an Rx receiver load (e.g., a battery charger) using near-field magnetic induction.

The CV90330supports Tx configurations such as described in the WPC\* v1.2.4 BPP & EPP power profile Tx specification. The CV90330also embedded QC2.0/QC3.0 Phy interface and Link engine.

Version 1.1

#### 7.1 Overview

The simplified block diagram of the CV90330is shown in Figure 3 and contains the following functions:

- Optimized and compliant support of WPC and High-Speed-Charger transmitter protocols.

- Supports WPC low power transmitter types with external MOSFET.

- Embedded 8-bits enhanced 8051core, with 20kBytes NVRAM .

- Supports high speed serial flash (SPI interface) for system development, application development, and troubleshooting.

- Dithered pulse-width modulation (PWM) controller for high resolution voltage modulation.

- Multiple enhanced demodulation schemes using fewer external components for robust communication.

- Built-in SPI and URAT interface to communicate with external devices.

- Built-in PLL and clock synthesizer for PWM generation and back channel communication.

- Supports variable logic I/O voltages with dedicated VDD pin.

- Built-in general purpose 12-bit, 100ksps ADC for temperature, voltage, current measurement, and signal processing.

- Two banks of GPIOs with a dedicated power supply.

#### 7.2 Overview of GPIO Usage

On the CV90330transmitter IC, there are two banks of GPIOs, P0 and P1 ports, which can be configured for various functions. P1.6 and P1.7 are configurable as GPIO or ADCs input.

### 7.3 ADC Considerations

ADC-Ch[0:5]can be connected internally to the successive-approximation 12-bit ADC via a multiplexed input. AD-Ch0 and AD-Ch[6:7]can be confederate as external ADCs , AD-Ch8 is connected to the 1.200 voltage reference source inside the chip.AD-Ch9 is connected to internal temperature sensor.

### 7.4 User Indicators

The CV90330supports a variety of options for notifying end-users of the charging status by configuring the GPIO port:

- A piezo-electric buzzer that is supported using GPIO and built-in Timer, which buzzes when the power transfer link is established

- LED visual indicators connected to the LED to notify users of various events

- Defined other status indicators by end-users.

#### 7.5 Over-Voltage and Over-Current Protection

The CV90330 integrates over-voltage protection (OVP) and over-current protection (OCP) shutdown protection including programmable thresholds. These thresholds are designed to protect the full-bridge and wireless receiver units from exposure to voltages and/or currents that could potentially cause damage or unexpected behavior from the system. For WPC A11 +5 VIN applications, the default OVP level is 6.5V, and this is only monitored during initial power startup. The default OCP level is 2.0A, and this is continuously monitored. The voltage is detected at the VIN pin, and the current is sensed across the R<sub>SENSE</sub> resistor. If the OCP threshold is exceeded during operation, the CV90330 will cease power transmission and will only resume normal operation after the receiver is removed and replaced on the charging pad or the Tx power is cycled. If an OVP event occurs during startup, the power must be cycled and remain below the OVP threshold during startup for normal operation to occur.

#### 7.6 Thermal Protection

The CV90330 integrates thermal overload shutdown circuitry to prevent damage resulting from excessive thermal stress that could be encountered under fault conditions. This circuitry will shut down or reset the device if the die temperature exceeds the thermal shutdown specification.

To allow the maximum possible load current and to prevent thermal overload, it is important to ensure that the heat generated by the CV90330solution is dissipated into the PCB. All the available pins must be soldered to the PCB. GND pins (especially the E-PAD) and the external bridge FETs should be soldered to the PCB ground or power planes to improve thermal performance with multiple vias connected to all layers of the PCB. For the QFN package, the exposed paddle (Thermal Pad) must be soldered to the PCB with multiple vias evenly distributed under the package and exiting the bottom side of the PCB. This improves heat flow away from the package and minimizes package thermal gradients.

#### 8. Description of the Wireless Power Charging System

A wireless power charging system has a base station with one or more transmitters that make power available DC-to-AC inverter(s) and transmit the power over a strongly-coupled inductor pair to a receiver in a mobile device. A WPC\* transmitter could be a *free-positioning* or *magnetically-guided* type. A *free-positioning* type of transmitter has a coil that gives limited spatial freedom to the end-user to align the receiver to the transmitter.

The amount of power transferred to the mobile device is controlled by the receiver. The receiver sends communication packets to the transmitter to increase power, decrease power, or maintain the power level. The communication is purely digital, and communication 1's and 0's ride on top of the power link that exists between the two coils.

A feature of wireless charging system is the fact that when they are not charging a mobile device, the transmitter is in a very-low-power sleep mode. The transmitter remains in this low-power mode and periodically pings until the transmitter detects the presence of a receiver; only after a valid receiver is detected does the transmitter enter the negotiation phase of operation and commence with power transfer.

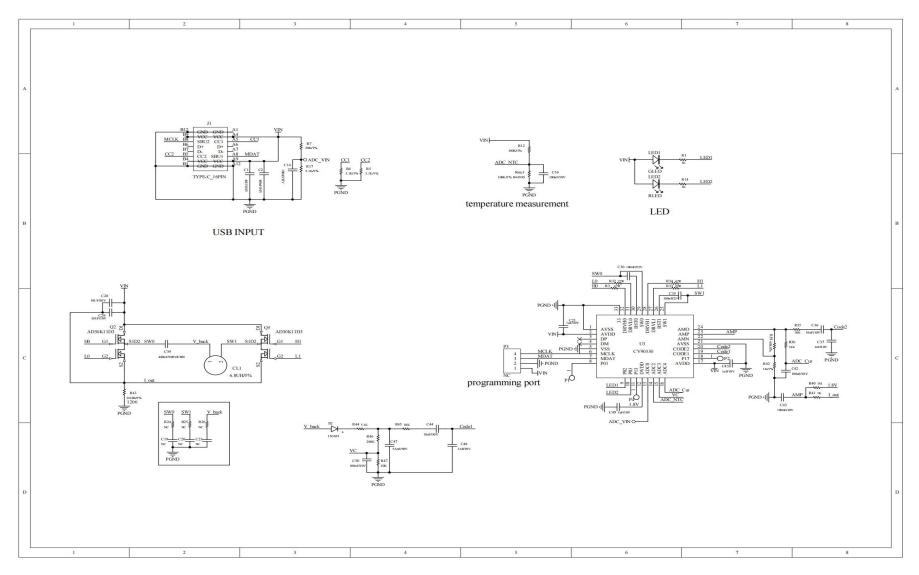

## **9.** Application Schematics

Version 1.1

10

#### **10.** Package Drawings